仅对英特尔可见 — GUID: wvo1486507372714

Ixiasoft

2.2.1. 选择和实例化PHY IP Core

2.2.2. PHY IP Core的配置

2.2.3. 生成PHY IP Core

2.2.4. PLL IP Core的选择

2.2.5. 配置PLL IP Core

2.2.6. PLL IP Core的生成

2.2.7. 复位控制器(Reset Controller)

2.2.8. 创建重配置逻辑

2.2.9. 将PHY IP连接到PLL IP Core和Reset Controller

2.2.10. 连接数据通路(Connect Datapath)

2.2.11. 模拟参数设置

2.2.12. 编译设计

2.2.13. 验证设计功能性

2.7.1. PIPE的收发器通道数据通路

2.7.2. 支持的PIPE特性

2.7.3. 如何连接PIPE Gen1和Gen2模式的TX PLL

2.7.4. 如何在 Cyclone® 10 GX收发器中实现PCI Express (PIPE)

2.7.5. PIPE的Native PHY IP参数设置

2.7.6. 用于PIPE的fPLL IP参数内核设置

2.7.7. 用于PIPE的ATX PLL IP参数设置

2.7.8. 用于PIPE的Native PHY IP端口

2.7.9. 用于PIPE的fPLL端口

2.7.10. 用于PIPE的ATX PLL端口

2.7.11. 如何对PIPE配置布局通道

2.9.1.1. 如何在 Cyclone® 10 GX收发器中实现基本(增强型PCS)收发器配置规则(Basic (Enhanced PCS) Transceiver Configuration Rules)

2.9.1.2. Basic (Enhanced PCS)的Native PHY IP参数设置

2.9.1.3. 如何在Basic Enhanced PCS中使能低延迟

2.9.1.4. 增强的PCS FIFO操作

2.9.1.5. TX数据比特滑移(TX Data Bitslip)

2.9.1.6. TX数据极性反转

2.9.1.7. RX数据比特滑移(RX Data Bitslip)

2.9.1.8. RX数据极性反转

2.9.2.1. 字对齐器手动模式(Word Aligner Manual Mode)

2.9.2.2. 字对齐器同步状态机模式

2.9.2.3. RX比特滑移(RX Bit Slip)

2.9.2.4. RX极性反转

2.9.2.5. RX比特反转(RX Bit Reversal)

2.9.2.6. RX字节反转(RX Byte Reversal)

2.9.2.7. 基本(单宽度)模式下的速率匹配FIFO

2.9.2.8. Rate Match FIFO Basic (Double Width)模式

2.9.2.9. 8B/10B编码器和解码器(8B/10B Encoder and Decoder)

2.9.2.10. 8B/10B TX差异控制

2.9.2.11. 如何在Basic模式下使能低延迟

2.9.2.12. TX比特滑移(TX Bit Slip)

2.9.2.13. TX极性反转

2.9.2.14. TX比特反转(TX Bit Reversal)

2.9.2.15. TX字节反转(TX Byte Reversal)

2.9.2.16. 如何在 Cyclone® 10 GX收发器中实现基本收发器配置规则和带速率匹配的基本收发器配置规则

2.9.2.17. Basic,速率匹配配置的Basic的Native PHY IP参数设置

6.1. 重新配置通道和PLL块

6.2. 与重配置接口进行交互

6.3. 配置文件

6.4. 多个重配置Profile

6.5. 嵌入式重配置Streamer

6.6. 仲裁

6.7. 动态重配置的建议

6.8. 执行动态重配置的步骤

6.9. 直接重配置流程

6.10. Native PHY IP或PLL IP核指导型重配置流程

6.11. 特殊情况的重配置流程

6.12. 更改PMA模拟参数

6.13. 端口和参数

6.14. 动态重配置接口跨多个IP块合并

6.15. 嵌入式调试功能

6.16. 使用数据码型生成器和检查器

6.17. 时序收敛建议

6.18. 不支持的功能

6.19. Cyclone® 10 GX收发器寄存器映射

8.7.1. XCVR_C10_TX_PRE_EMP_SIGN_PRE_TAP_1T

8.7.2. XCVR_C10_TX_PRE_EMP_SIGN_PRE_TAP_2T

8.7.3. XCVR_C10_TX_PRE_EMP_SIGN_1ST_POST_TAP

8.7.4. XCVR_C10_TX_PRE_EMP_SIGN_2ND_POST_TAP

8.7.5. XCVR_C10_TX_PRE_EMP_SWITCHING_CTRL_PRE_TAP_1T

8.7.6. XCVR_C10_TX_PRE_EMP_SWITCHING_CTRL_PRE_TAP_2T

8.7.7. XCVR_C10_TX_PRE_EMP_SWITCHING_CTRL_1ST_POST_TAP

8.7.8. XCVR_C10_TX_PRE_EMP_SWITCHING_CTRL_2ND_POST_TAP

仅对英特尔可见 — GUID: wvo1486507372714

Ixiasoft

4.3.2. Model 2: 确认模型

确认模型使用事件驱动(event-driven)机制。该模型被用于具有严格时间要求的应用。必须等待接收来自发器Native PHY IP核的确认,以确保成功地置位或解除置位模拟复位,而不是等待至少70 μs的tx_analogreset和rx_analogreset置位时间。

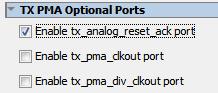

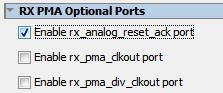

要使能确认模型,可使能收发器Native PHY IP核中的端口如下:

- 使能TX PMA中的tx_analog_reset_ack端口

图 152. Enabling the tx_analog_reset_ack Port

- 使能RX PMA中的rx_analog_reset_ack端口

图 153. Enabling the rx_analog_reset_ack Port

注:

必须将tx_analog_reset_ack和rx_analog_reset_ack视为异步信号。将它们发送至控制逻辑之前,避居将它们传递给同步器。