仅对英特尔可见 — GUID: mtr1430270862294

Ixiasoft

仅对英特尔可见 — GUID: mtr1430270862294

Ixiasoft

2.4.2.6. Read-Modify-Write存储器

Intel® Hyperflex™ 体系结构FPGA M20K存储器模块支持一致性读取(coherent read)以简化实现read-modify-write存储器。read-modify-write在诸如网络统计计数器之类的应用中很有用。对于将一个值存储在存储器中的应用,read-modify-write存储器也是很有用的,这类应用要求在单一周期内递增和重写。

M20K存储模块通过消除对手写高速缓存电路的需求而简化了实现。由于高时钟速度或者大型计数器,在多个时钟周期上对修改操作进行流水线化的高速缓存电路变得复杂。

要使用一致性读取功能,需根据是否寄存输出数据端口来连接存储器。如果寄存输出数据端口,则要在例化存储器时将两个寄存器阶段添加到写使能和写地址行。

如果没有寄存输出数据端口,那么要在例化存储器时将一个寄存器阶段添加到写使能和写地址行。

一致性读取(coherent read)的使用有如下限制:

- 必须使用相同的时钟进行读写。

- 必须对读端口和写端口使用相同的宽度。

- 不能使用ECC。

- 不能使用字节使能。

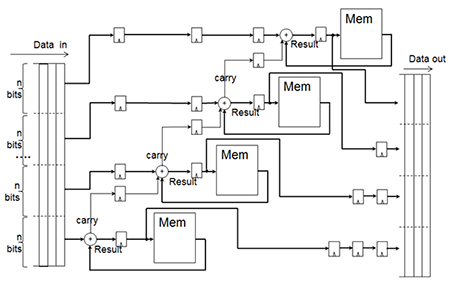

流水线化Read-Modify-Write存储器显示了read-modify-write存储器的流水线方法,此方法可以提高性能,而无需维护用于跟踪最近活动的高速缓存。

如果您需要与一致性读取不兼容的M20K存储器功能,或者如果您不想使用一致性读取,那么请使用以下替代方法来提高存储器的fMAX性能:

- 将修改操作分成能够在一个周期内完成的更小模块。

- 确保每个块(chunk)不能宽于一个M20K存储器模块。Compiler将数据字分成多个n-bit块(chunk),其中每个块(chunk)都足够小,以便在一个时钟周期内进行高效处理。

- 要增加fMAX,则需要增加存储器模块的数量,使用更窄的存储器模块并增加延迟。要降低延迟,则需要使用更少,更宽的存储器模块,并且适当地移除流水线级。由于read-modify-write电路的性质,read-modify-write电路中的环路是不可避免的,但此解决方案中的环路小而短。此解决方案是可伸缩的,因为无论流水线级的数量是多少,基本结构总保持不变。