仅对英特尔可见 — GUID: lfb1468436589960

Ixiasoft

2.4.2.1. 高速时钟域(High-Speed Clock Domains)

2.4.2.2. 重构环路(Restructuring Loops)

2.4.2.3. 控制信号反压(Control Signal Backpressure)

2.4.2.4. 使用FIFO状态信号的流程控制

2.4.2.5. 包含skid缓冲器的流程控制

2.4.2.6. Read-Modify-Write存储器

2.4.2.7. 计数器和累加器

2.4.2.8. 状态机

2.4.2.9. 储存器

2.4.2.10. DSP模块

2.4.2.11. 一般逻辑

2.4.2.12. 求模与除法

2.4.2.13. 复位

2.4.2.14. 硬件重用

2.4.2.15. 算法要求

2.4.2.16. FIFO

2.4.2.17. 三元加法器(Ternary Adders)

5.2.1. 不足的寄存器(insufficient Registers)

5.2.2. 短路径/长路径(short path/long path)

5.2.3. 快进限制(Fast Forward Limit)

5.2.4. 环路(loop)

5.2.5. 每个时钟域一个关键链

5.2.6. 相关时钟组中的关键链

5.2.7. 复杂的关键链

5.2.8. 延伸到可定位的节点

5.2.9. 域边界入口和域边界出口(Domain Boundary Entry and Domain Boundary Exit)

5.2.10. 包括双时钟存储器的关键链

5.2.11. 关键链比特和总线

5.2.12. 延迟线

仅对英特尔可见 — GUID: lfb1468436589960

Ixiasoft

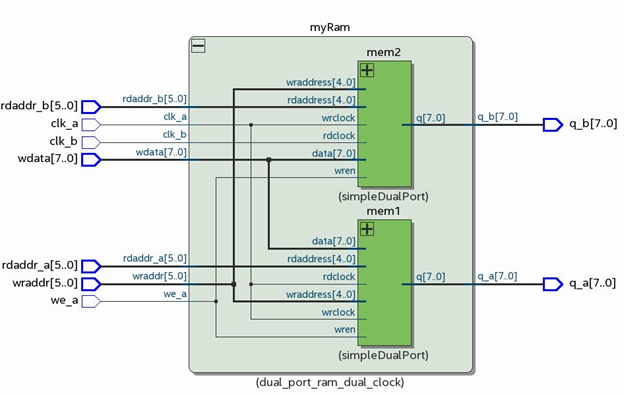

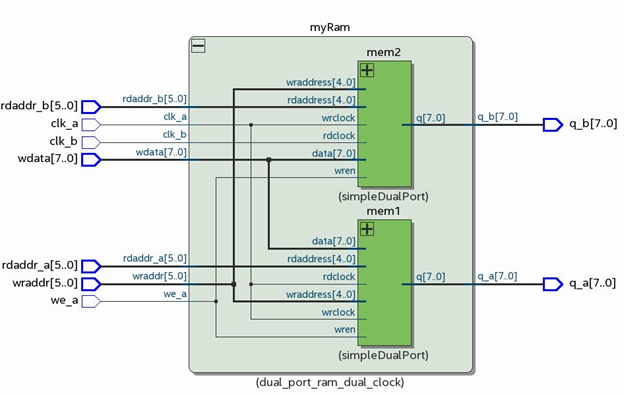

2.4.2.9.3. Intel® Hyperflex™ 体系结构简单双端口存储器示例

使用两个简单的双端口存储器可以将器件中的M20K模块的使用率翻倍。然而,此存储器结构可以在高达1 GHz的频率上运行。当在 Intel® Hyperflex™ 体系结构FPGA中使用包括独立时钟的真双端口存储器时,此频率是不可能的。

图 74. 简单双端口存储器实现

通过推断RTL中的简单双端口存储器可以实现类似的频率结果,而不是通过 英特尔® Quartus® Prime IP parameter editor中的实例来实现类似的频率结果。

简单双端口RAM接口

module simple_dual_port_ram_with_SDPs #(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=6) ( input [(DATA_WIDTH-1):0] wrdata, input [(ADDR_WIDTH-1):0] wraddr, rdaddr, input we_a, wrclock, rdclock, output reg [(DATA_WIDTH-1):0] q_a ); // Declare the RAM variable reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0]; always @ (posedge wrclock) begin // Port A is for writing only if (we_a) begin ram[wraddr] <= wrdata; end end always @ (posedge rdclock) begin // Port B is for reading only begin q_a <= ram[rdaddr]; end end endmodule

真双端口RAM行为仿真

module test (wrdata, wraddr, rdaddr_a, rdaddr_b, clk_a, clk_b, we_a, q_a, q_b); input [7:0] wrdata; input clk_a, clk_b, we_a; input [5:0] wraddr, rdaddr_a, rdaddr_b; output [7:0] q_a, q_b; simple_dual_port_ram_with_SDPs myRam1 ( .wrdata(wrdata), .wraddr(wraddr), .rdaddr(rdaddr_a), .we_a(we_a), .wrclock(clk_a), .rdclock(clk_b), .q_a(q_a) ); simple_dual_port_ram_with_SDPs myRam2 ( .wrdata(wrdata), .wraddr(wraddr), .rdaddr(rdaddr_b), .we_a(we_a), .wrclock(clk_a), .rdclock(clk_a), .q_a(q_b) ); endmodule