仅对英特尔可见 — GUID: byt1544211282780

Ixiasoft

2.4.2.1. 高速时钟域(High-Speed Clock Domains)

2.4.2.2. 重构环路(Restructuring Loops)

2.4.2.3. 控制信号反压(Control Signal Backpressure)

2.4.2.4. 使用FIFO状态信号的流程控制

2.4.2.5. 包含skid缓冲器的流程控制

2.4.2.6. Read-Modify-Write存储器

2.4.2.7. 计数器和累加器

2.4.2.8. 状态机

2.4.2.9. 储存器

2.4.2.10. DSP模块

2.4.2.11. 一般逻辑

2.4.2.12. 求模与除法

2.4.2.13. 复位

2.4.2.14. 硬件重用

2.4.2.15. 算法要求

2.4.2.16. FIFO

2.4.2.17. 三元加法器(Ternary Adders)

5.2.1. 不足的寄存器(insufficient Registers)

5.2.2. 短路径/长路径(short path/long path)

5.2.3. 快进限制(Fast Forward Limit)

5.2.4. 环路(loop)

5.2.5. 每个时钟域一个关键链

5.2.6. 相关时钟组中的关键链

5.2.7. 复杂的关键链

5.2.8. 延伸到可定位的节点

5.2.9. 域边界入口和域边界出口(Domain Boundary Entry and Domain Boundary Exit)

5.2.10. 包括双时钟存储器的关键链

5.2.11. 关键链比特和总线

5.2.12. 延迟线

仅对英特尔可见 — GUID: byt1544211282780

Ixiasoft

2.2.7.3.1. 实现时钟门控(Implementing Clock Gating)

若要实现时钟门控,请使用 英特尔® Quartus® Prime软件中的以下 英特尔® FPGA IP对USER_CLKGATE信号进行访问:

- Reset Release 英特尔® FPGA IP—在配置完成前将设计保持在复位状态(通过门控时钟,复位或者写使能)。此IP输出nINIT_DONE信号。当nINIT_DONE为低电平时,器件不再处于配置模式。

- Clock Control 英特尔® FPGA IP—使用反向的nINIT_DONE信号作为时钟使能信号。

请按照以下步骤实现时钟门控:

- 在 英特尔® Quartus® Prime软件中打开一个设计。

- 在IP Catalog中,在搜索域中输入reset release,然后双击Reset Release 英特尔® FPGA IP 。

- 在参数编辑器中对配置指定相应的参数,然后点击Generate HDL。

- 重复步骤2到3将Clock Control 英特尔® FPGA IP添加到工程中。在IP生成之前,在参数编辑器中对IP指定以下选项:

- 在Clock Gating下,开启Clock Enable选项。

- 对Clock Enable Type选择Root Level。

- 对Enable Register Mode选择Negative Latch。

- 将Reset Release和Clock Control 英特尔® FPGA IP连接在一起:

- 要门控时钟,请使用反相的nINIT_DONE作为Clock Control 英特尔® FPGA IP的使能输入。

- 如果要求初始条件,那么Intel建议Clock Control 英特尔® FPGA IP也使用根时钟门控(root clock gating)。

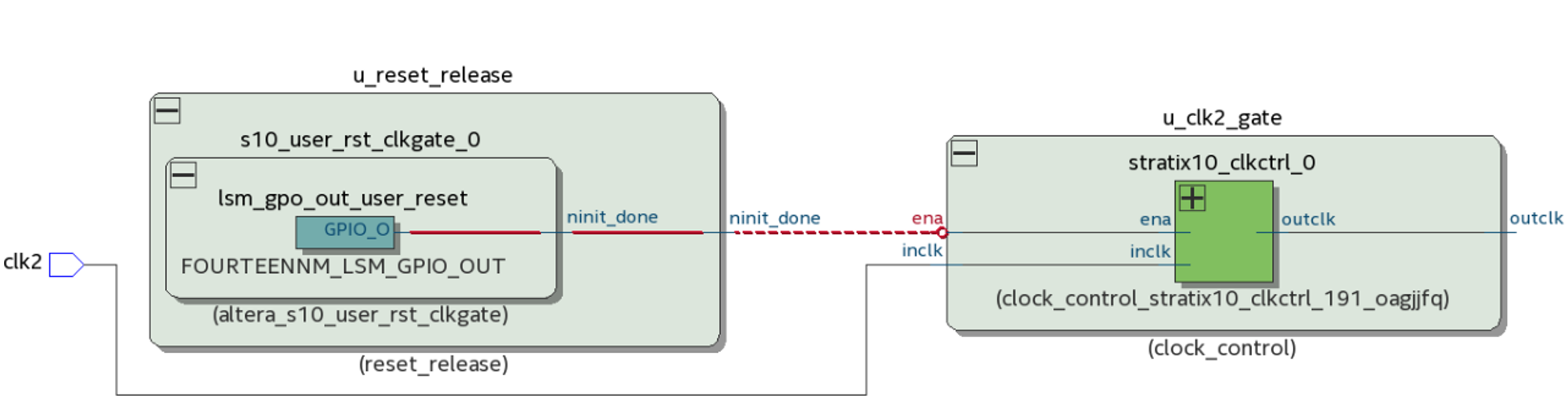

下图显示了Reset Release与Clock Control 英特尔® FPGA IP之间的正确连接,确保配置后的准确初始条件:

图 19. Reset Release (reset_release)与Clock Control (clock_control) 英特尔® FPGA IP Core之间的连接

Clock Control 英特尔® FPGA IP使用ena信号执行时钟门控功能。Clock Control 英特尔® FPGA IP的输出上的时钟信号然后可以安全地用于已初始化的寄存器(ALM and Hyper-Registers)。