仅对英特尔可见 — GUID: rnx1484851394957

Ixiasoft

仅对英特尔可见 — GUID: rnx1484851394957

Ixiasoft

3.1.1.2. 将ATX PLL用于GXT通道

- Main ATX PLL配置成一个发送PLL

- 相邻的顶部ATX PLL配置成一个GXT时钟缓冲器,将中心ATX PLL的串行时钟传递到相邻的GXT通道

- 相邻的底部ATX PLL配置成一个GXT时钟缓冲器, 将中心ATX PLL的串行时钟传递到相邻的GXT通道

如果需要2个GXT通道并且它们与发送ATX PLL相邻(一个bank中的通道0和1和发送ATX PLL位于bank的底部,或者一个bank中的通道3和4和发送ATX PLL位于bank的顶部),那么不需要GXT时钟缓冲器ATX PLL。如果需要一个GXT通道,那么同一规则适用。

如果需要4个GXT通道并且它们是相邻的(一个bank中的通道0,1,3,4或者一个bank中的通道0和1, 下面bank中的通道3和4),那么需要一个GXT时钟缓冲器ATX PLL。发送ATX PLL可以是与顶部或底部2个GXT通道相邻的ATX PLL。 如果需要3个GXT通道,那么同一规则适用。

GXT通道的参考时钟必须位于与master ATX PLL相同的三元组中。

- 发送和GXT时钟缓冲器ATX PLL上的tx_serial_clk_gxt输出端口。tx_serial_clk_gxt连接到 Intel® Stratix® 10 L-Tile/H-Tile Native PHY IP中的tx_serial_clk端口。

- 配置成发送PLL的ATX PLL上的gxt_output_to_abv_atx输出端口,输出GXT串行时钟到配置成GXT时钟缓冲器的above ATX PLL。

- 配置成发送PLL的ATX PLL上的gxt_output_to_blw_atx输出端口,输出GXT串行时钟到配置成GXT时钟缓冲器的below ATX PLL。

- 配置成GXT时钟缓冲器的 ATX PLL上的gxt_input_from_blw_atx输入端口,从配置为发送PLL的below ATX PLL输入GXT串行时钟。

- 配置成GXT时钟缓冲器的 ATX PLL上的gxt_input_from_abv_atx输入端口,从配置为发送PLL的above ATX PLL输入GXT串行时钟。

发送ATX PLL的端口gxt_output_to_abv_atx需要连接到above GXT clock buffer ATX PLL的端口gxt_input_from_blw_atx。

发送ATX PLL的端口gxt_output_to_blw_atx需要连接到below GXT clock buffer ATX PLL的端口gxt_input_from_abv_atx。

- GXT transmit PLL with GXT clocks to adjacent GXT channels

- GXT transmit PLL with GXT clocks to GXT clock buffer ATX PLLs

- GXT transmit PLL with GXT clocks to adjacent GXT channels and GXT clock buffer ATX PLLs

- GXT clock buffer ATX PLL

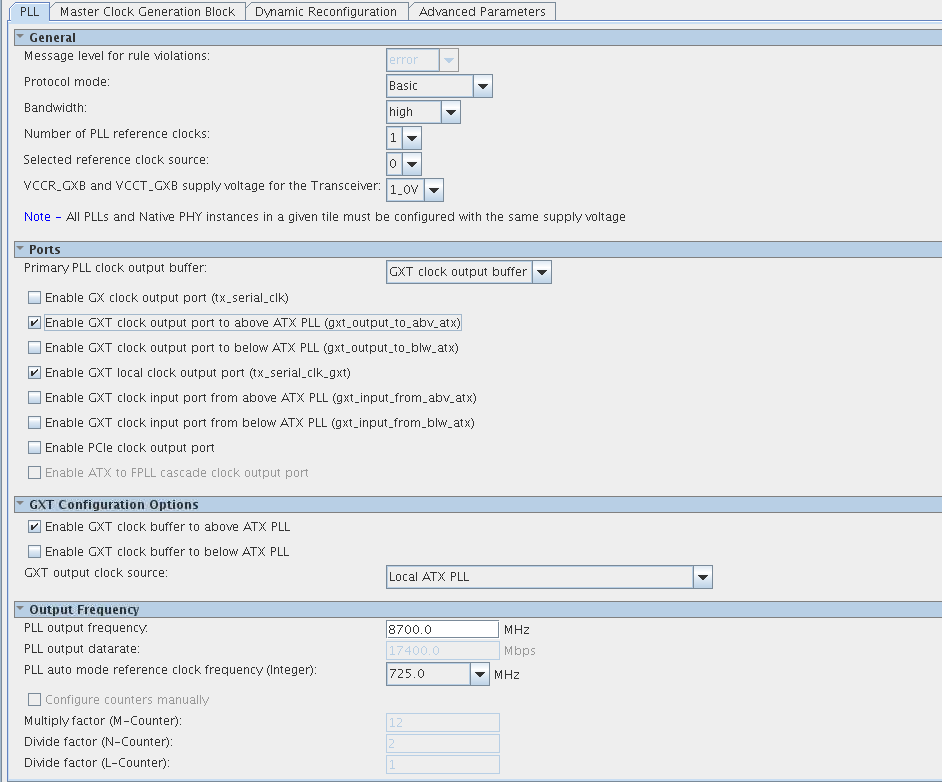

- 将ATX PLL operation mode drop-down设置成GXT mode。

- 选择Enable GXT local clock output port (tx_serial_clk_gxt)复选框。

- 将GXT output clock source drop-down设置成Local ATX PLL。

- 设置ATX PLL输入参考时钟和数据速率参数。

- 将ATX PLL operation mode drop-down设置成GXT mode。

- 选择Enable GXT clock output port to above ATX PLL (gxt_output_to_abv_atx), Enable GXT clock output port to below ATX PLL (gxt_output_to_blw_atx),或者两个都选。

- 选择Enable GXT clock buffer to above ATX PLL, Enable GXT clock buffer to above ATX PLL,或者两个都选。

- 将GXT output clock source drop-down设置成Disabled。

- 设置ATX PLL输入参考时钟和数据速率参数。

- 将ATX PLL operation mode drop-down设置成GXT mode。

- 选择Enable GXT local clock output port (tx_serial_clk_gxt) 复选框。

- 将GXT output clock source drop-down设置成Local ATX PLL。

- 选择Enable GXT output port to above ATX PLL (gxt_output_to_abv_atx), Enable GXT output port, or both to below ATX PLL (gxt_output_to_blw_atx)复选框。

- 选择Enable GXT clock buffer to above ATX PLL, Enable GXT clock buffer, or both to above ATX PLL复选框。

- 设置ATX PLL输入参考时钟和数据速率参数。

- 将ATX PLL operation mode drop-down设置成GXT mode。

- 选择Enable GXT local clock output port (tx_serial_clk_gxt)复选框。

- 将GXT output clock source drop-down设置成Input from ATX PLL above (gxt_input_from_abv_atx)或者Input from ATX PLL below (gxt_input_from_blw_atx)。

- 将pll_refclk0管脚连接到REFCLK管脚,如果GXT clock buffer ATX PLL没有重配置成一个GXT transmit PLL或者GX transmit PLL。

ATX PLL可以在模式之间重新配置,但必须在实例中使能所有需要的端口。