仅对英特尔可见 — GUID: szw1597163141403

Ixiasoft

仅对英特尔可见 — GUID: szw1597163141403

Ixiasoft

2.5.1.17. Report Pipelining Information(报告流水线信息)

Report Pipelining Information...不会在建议的流水线阶段调整中执行任何功能性分析。您必须意识到删除流水线阶段可能会引起潜在的功能性变化。可能存在所有寄存器流水线中的阶段对功能性而言都是必要的情况。此报告可帮助识别具有比覆盖距离所需的寄存器更多的位置。

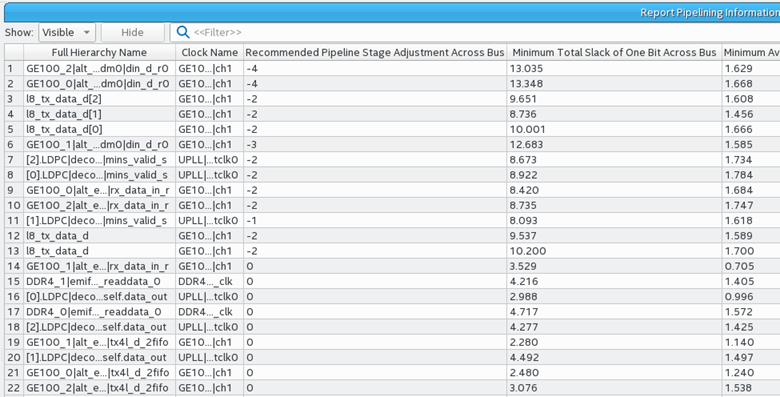

这个详细报告以树状结构显示每个寄存器。关于过度或不足的流水线建议位于主报告中。下图以树形结构显示了总线链内的每个寄存器:

为帮助识别潜在的过度流水线,Report Pipelining Information报告:

- 推荐的跨总线流水线阶段调整

- 跨总线的最小总时序裕量为1比特

- 跨总线的最小平均时序裕量为1比特

- 寄存器之间的距离

- 您设计中总线的宽度

- 连续寄存器的数量

- 总线上的寄存器数量

Recommended Pipeline Stage Adjustment Across Bus报告您可以从总线上为每个比特移除的寄存器数量。Average Distance Per Stage,Max Distance Per Stage和Min Distance Per Stage栏报告在逻辑阵列模块(LAB)中测量的曼哈顿(Manhattan)距离。Bus Average Depth,Bus Max Depth和Bus Min Depth栏报告顺序的,单扇出寄存器的数量。对于有一个以上时钟源的寄存器,报告列出了最快的一个。

Recommended Pipeline Stage Adjustment Across Bus栏下的1+符号意味着总线可能需要添加更多寄存器来满足时序要求。请参考Fast Forward Timing Closure Recommendations报告。

如果此报告识别出一个有多个顺序寄存器的大型寄存器链,并且寄存器之间的距离很短,那么这种情况可能表明存在过度流水线。您也许可以删除一些寄存器来恢复一些器件区域并减少拥塞。

以下选项可用于此报告:

| 选项 | 可用设置 |

|---|---|

| Pipeline | 指定报告一个寄存器流水线的阈值。您可以对此报告包含的Minimum average bus depth,Minimum bus width和Maximum number of rows进行定义。 |

| Report panel name | 指定报告面板的名称。您可以选择使能File name,将信息写入到一个文件中。如果您将.htm或者.html作为后缀,那么Timing Analyzer会生成HTML格式的报告。如果您使能File name,那么您可以使用最新的数据覆盖Overwrite文件或者添加后缀Append。 |

| Tcl command | 显示与所选的GUI选项对应的Tcl语法。您可以将命令从Console复制到Tcl文件中。 |