仅对英特尔可见 — GUID: mwh1410383855277

Ixiasoft

2.5.1.1. Report Fmax Summary(报告Fmax汇总)

2.5.1.2. Report Timing(报告时序)

2.5.1.3. Report Timing By Source Files(按源文件报告时序)

2.5.1.4. Report Data Delay(报告数据延迟)

2.5.1.5. Report Net Delay(报告网络延迟)

2.5.1.6. Report Clocks and Clock Network(报告时钟和时钟网络)

2.5.1.7. Report Clock Transfers(报告时钟传输)

2.5.1.8. Report Metastability(报告亚稳定性)

2.5.1.9. Report CDC Viewer(报告CDC Viewer)

2.5.1.10. Report Asynchronous CDC(报告异步CDC)

2.5.1.11. Report Logic Depth(报告逻辑深度)

2.5.1.12. Report Neighbor Paths(报告相邻路径)

2.5.1.13. Report Register Spread

2.5.1.14. Report Route Net of Interest

2.5.1.15. Report Retiming Restrictions(报告重定时限制)

2.5.1.16. Report Register Statistics(报告寄存器统计)

2.5.1.17. Report Pipelining Information(报告流水线信息)

2.5.1.18. 报告时间借用数据

2.5.1.19. Report Exceptions and Exceptions Reachability(报告异常和异常可达性)

2.5.1.20. Report Bottlenecks(报告瓶颈)

仅对英特尔可见 — GUID: mwh1410383855277

Ixiasoft

2.6.8.5.2. End Multicycle Setup = 2 and End Multicycle Hold = 0

在此示例中,结束多周期设置约束值为2,并且结束多周期保持约束值为0。

多周期约束

set_multicycle_path -from [get_clocks clk_src] -to [get_clocks clk_dst] \

-setup -end 2

注: Timing Analyzer不需要结束多周期保持值(end multicycle hold value),因为默认的结束多周期保持值为零。

在此示例中,通过将锁存沿移到下一个锁存沿,设置关系放宽(relax)一整个时钟周期。保持分析不会从默认设置更改。以下显示了Timing Analyzer执行的分析的设置时序图。锁存沿比默认的单周期分析晚一个时钟周期。

图 130. 设置时序图下图显示了Timing Analyzer执行的分析的设置时序图。在没有多周期约束的情况下,锁存沿是edge 1。然而,在有多周期约束的情况下,锁存沿是edge 2。

图 131. Setup Check计算

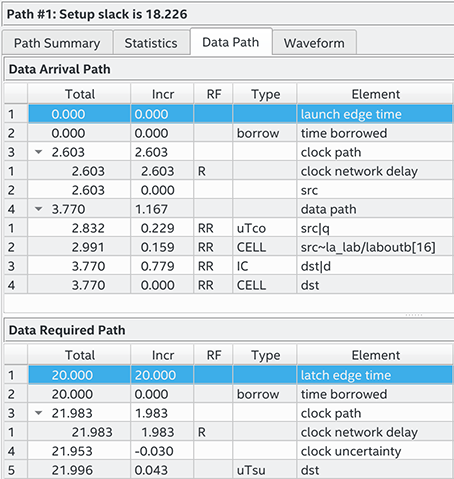

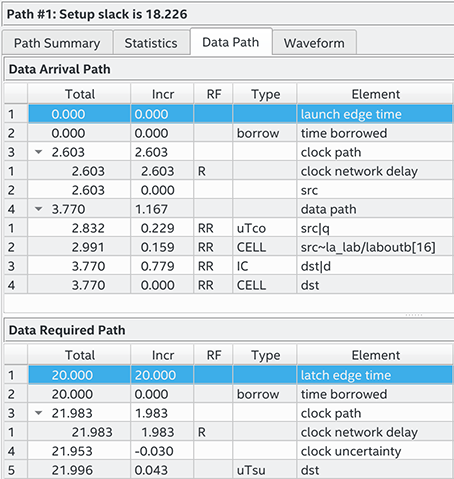

结束多周期设置约束(end multicycle setup assignment)为2的最具限制性的设置关系是20 ns。下图显示了Timing Analyzer中的设置报告,并突出显示了启动沿和锁存沿。

图 132. 包括设置多周期异常的设置报告

由于多周期保持锁存沿和启动沿与使用默认设置的保持分析结果相同,因此本示例中的多周期保持分析等效于单周期保持分析。保持检查与设置检查有关。通常,Timing Analyzer会对每个可能的设置检查执行保持检查,而不仅仅是在最具限制性的设置检查沿上执行保持检查。

图 133. 保持时序图下图显示了保持锁存沿现在是10和20 ns,而不是0和10 ns。

图 134. 包括设置多周期异常的保持报告

图 135. Hold Check计算