仅对英特尔可见 — GUID: pwi1556909661231

Ixiasoft

2.1. 何时使用Netlist Viewer:分析设计问题

2.2. 使用Netlist Viewers的 Intel® Quartus® Prime设计流程

2.3. RTL Viewer概述

2.4. Technology Map Viewer概述

2.5. Netlist Viewer用户接口

2.6. 原理图视图

2.7. 交叉探查Source Design File和其他 Intel® Quartus® Prime Windows

2.8. 从其他 Intel® Quartus® Prime窗口交叉探查Netlist Viewer

2.9. 查看时序路径

2.10. 优化设计网表修订历史

2.6.1. 以多选项卡视图显示原理图

2.6.2. 原理图符号

2.6.3. 在Schematic View中选择项目

2.6.4. Schematic View中的快捷菜单命令

2.6.5. 原理图中进行过滤

2.6.6. 在Schematic View中查看节点内容

2.6.7. 在Schematic View中移动节点

2.6.8. 在Technology Map Viewer中查看LUT表达

2.6.9. 缩放控制

2.6.10. Bird's Eye View导览

2.6.11. 原理图分页

2.6.12. 关注原理图页面中的网络

2.6.13. 维护Resource Property Viewer中的选择

5.6.5.1. 优化源代码

5.6.5.2. 改善Register-to-Register时序

5.6.5.3. 物理综合优化

5.6.5.4. 关闭Extra-Effort Power优化设置

5.6.5.5. 优化关于速度而非面积的综合

5.6.5.6. 综合期间展开层级结构

5.6.5.7. Synthesis Effort设置为High

5.6.5.8. 复制用于扇出控制的寄存器

5.6.5.9. 防止Shift Register推断

5.6.5.10. 使用Synthesis Tool中的其他可用综合选项

5.6.5.11. Fitter Seed

5.6.5.12. 将Router Timing Optimization设置为Maximum

6.3.1. 在Chip Planner中查看Logic Lock区域之间的连接

6.3.2. Logic Lock区域

6.3.3. Logic Lock区域的属性

6.3.4. Intel® Quartus® Prime Standard Edition和 Intel® Quartus® Prime Pro Edition间的约束移植

6.3.5. 创建Logic Lock区域

6.3.6. 定制Logic Lock区域的形状

6.3.7. 将器件资源放入Logic Lock区域

6.3.8. 层次型区域

6.3.9. 其他 Intel® Quartus® Prime Logic Lock设计功能

6.3.10. Logic Lock区域窗口

6.3.11. 插入区域(Snapping to a Region)

仅对英特尔可见 — GUID: pwi1556909661231

Ixiasoft

6.3.11. 插入区域(Snapping to a Region)

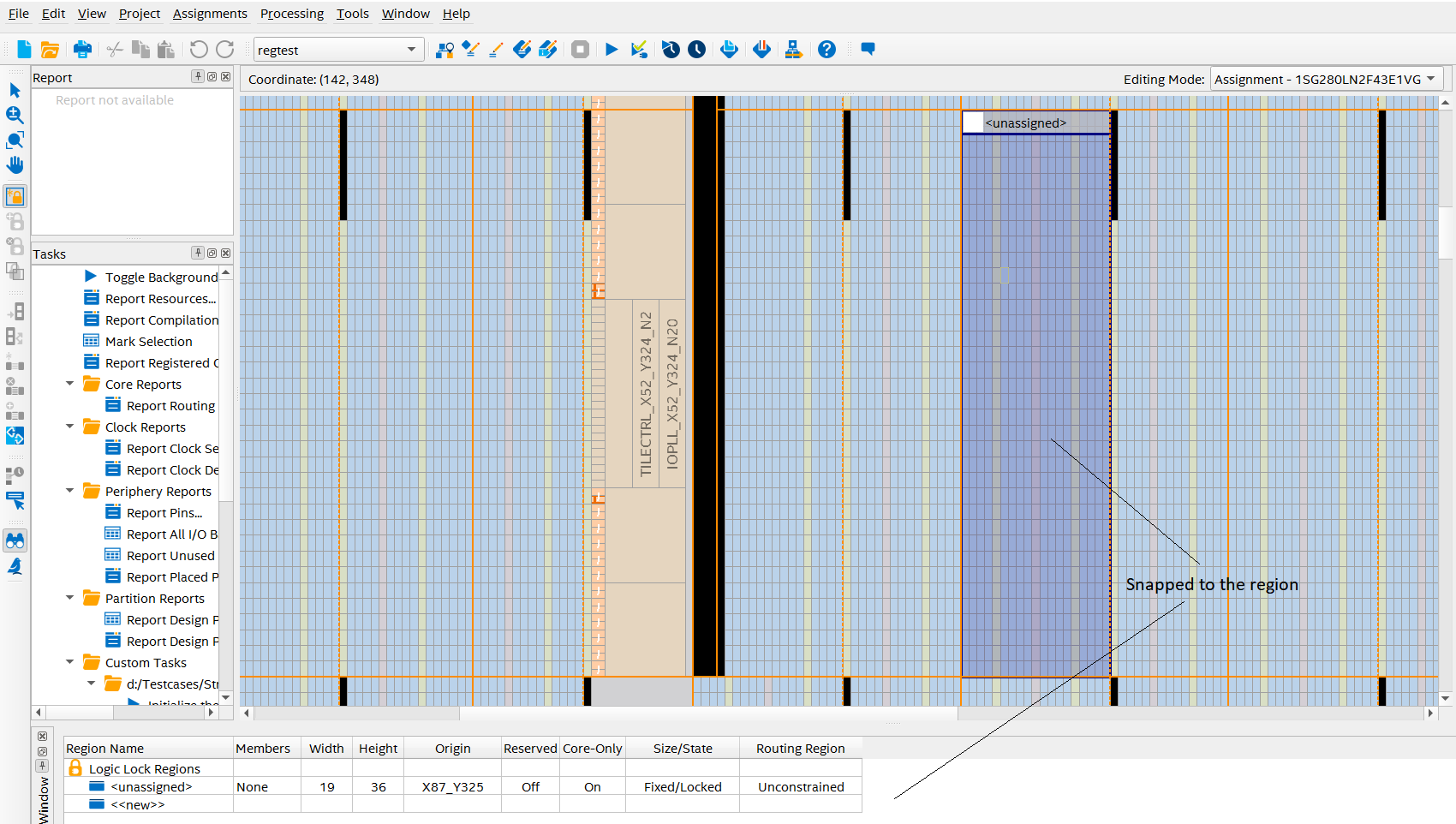

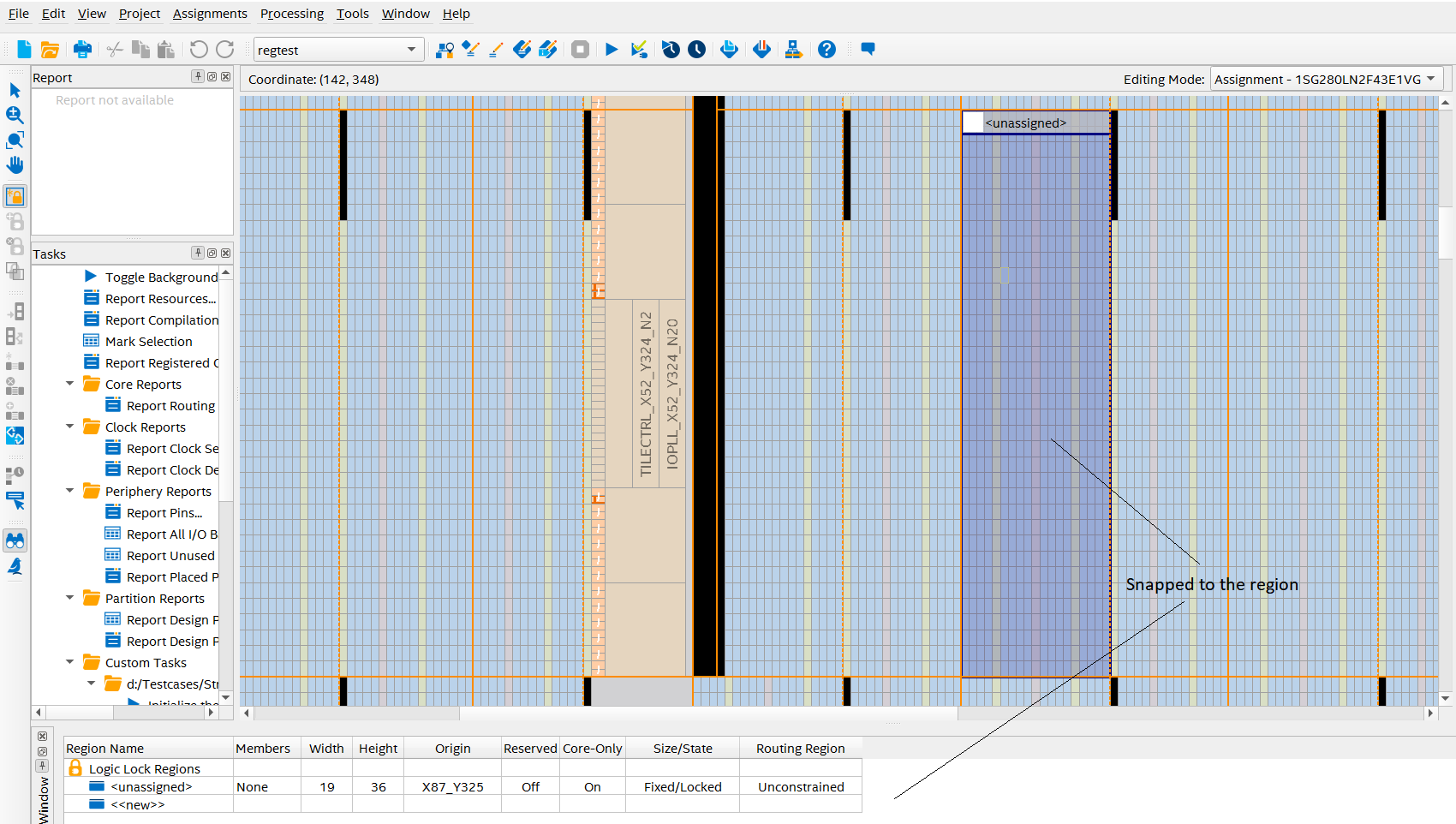

Chip Planner支持Logic Lock区域插入逻辑阵列块(snap-to-lab),其中所创建Logic Lock区域总是被插入逻辑阵列块。该操作适用于 Intel® Arria® 10中的时钟区域和Intel® Agilex® FPGA,以及Intel® Stratix® 10 FPGA中的时钟扇区。

默认情况下,Logic Lock区域始终被插入lab(逻辑阵列块)。可更改默认设置,点击View > Logic Lock Regions > Snap Logic Lock Region to

注: 如下图所示,在Logic Lock区域中执行如下操作,(如,创建,调整区域大小,或移动区域)或插入时钟区域(snap-to-clock-region)时,可查看时钟区域或扇区(具有橙色边界)。

图 64. 已插入区域

插入区域后,Logic Lock区域边界显示为交互模式。并可观察如下行为:

- Creating Region:单击鼠标左键创建Logic Lock区域。释放鼠标后,所创建的Logic Lock区域插入包含的时钟区域或扇区。

- Resize region (and resize diagonal):单击鼠标左键并拖动Logic Lock区域柄。释放鼠标后,Logic Lock区域调整大小并插入包含的时钟区域或扇区。

- Move region:选择并拖动Logic Lock区域以高亮显示时钟区域边界。释放鼠标按键后,Logic Lock区域移动到新的位置并插入包含的时钟区域或扇区。

- Same place and route regions are moved(相同位置和布线区域被移动):两个Logic Lock区域移动并插入包含的时钟扇区。

- Only place | route region is moved(仅位置 | 布线区域被移动):选定区域移动并插入时钟扇区,如果区域的新位置或大小不符合“place bboxes contained within route bboxes”(布线bbox中包含布局bbox)规则,则会警告提示。

- Subtract or make a hole:在snap-to-clock-region模式中执行减法时,可在插入区域的时钟区域或扇区中创建一个区域,然后减去。