仅对英特尔可见 — GUID: azl1475769383630

Ixiasoft

2.7. 仿真测试台

仿真测试台仿真DisplayPort TX串行环回到RX 。

注: 当前版本不支持DisplayPort 2.0仿真测试台。

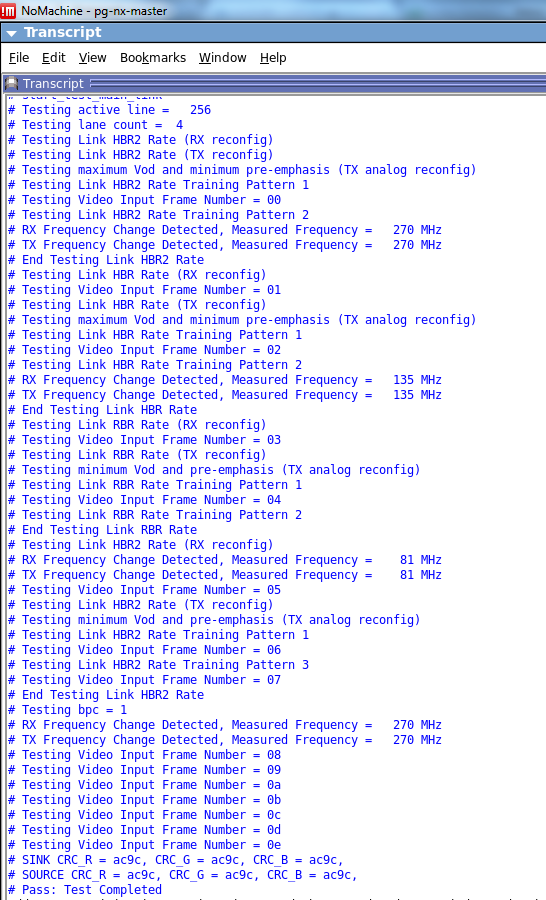

图 10. DisplayPort英特尔®FPGA IP单工模式仿真测试台结构框图

| 组件 | 描述 |

|---|---|

| Video Pattern Generator | 此生成器生成您可以配置的彩条模式。您可以参数化视频格式时序。 |

| 测试台控制 | 该模块控制仿真的测试序列并对TX内核生成必要的干预信号。 测试台控制块还从源和接收器读取CR 值以进行比较。 |

| RX Link Speed Clock Frequency Checker | 此检查器验证RX收发器恢复的时钟频率是否与所需的数据速率匹配。 |

| TX Link Speed Clock Frequency Checker | 此检查器验证TX收发器恢复的时钟频率是否与所需的数据速率匹配。 |

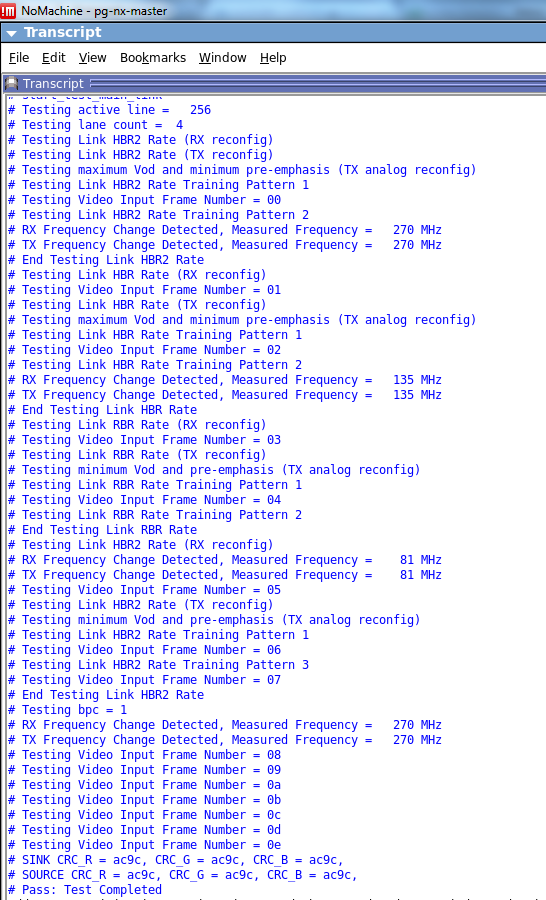

仿真测试台执行以下验证:

| 测试标准 | 验证 |

|---|---|

|

集成Frequency Checker以测量从TX和RX收发器输出的Link Speed时钟频率。 |

|

|

成功的仿真会以如下消息结束:

| 仿真器 | 支持的平台 | 支持的语言 |

|---|---|---|

| Riviera-PRO* | Windows/Linux | VHDL和Verilog HDL |

| ModelSim* | Windows/Linux | VHDL和Verilog HDL |

| Xcelium* Parallel | Linux | Verilog HDL |

| VCS* / VCS* MX | Linux | VHDL和Verilog HDL |