仅对英特尔可见 — GUID: jba1435006412949

Ixiasoft

仅对英特尔可见 — GUID: jba1435006412949

Ixiasoft

1.6.13. 综述设计研究中电容器的节省

| PDN设计阶段 |

VCC Feffective (MHz) |

所需的VCC Caps |

VCCR_GXB Caps |

VCCT_GXB Caps |

|---|---|---|---|---|

| 原始叠层,所有电源在L18,# PWR/GND vias = 50 |

10.62 |

>301 |

>301 |

>301 |

| 已更正的# PWR/GND过孔和分层号 已减低用于VCC传导电感 已增加用于VCCR_GXB & VCCT_GXB 的传导电感 已减低用于VCC,VCCR_GXB,VCCT_GX 的垂直电感 |

30.68 |

>301 |

>301 |

>301 |

| 移动电源来优化分层使更靠近FPGA放置从而减低垂直电感 |

35.61 |

>301 |

>301 |

>301 |

| 将平面移动至相互靠近以提高高频电容 |

36.71 |

>301 |

>301 |

239 |

| 将去耦电容放置到顶层表面以减少垂直电感 |

36.71 |

>301 |

255 |

180 |

| 使用低ESL X2Y caps以减少电容贴装电感 |

36.71 |

>301 |

28 |

22 |

| 使用低ESR大容量caps以提高低频性能 |

36.71 |

>301 |

23 |

17 |

| 使用内核时钟频率和电流上升周期参数减少VCC高频需求 |

36.71 |

37 |

23 |

17 |

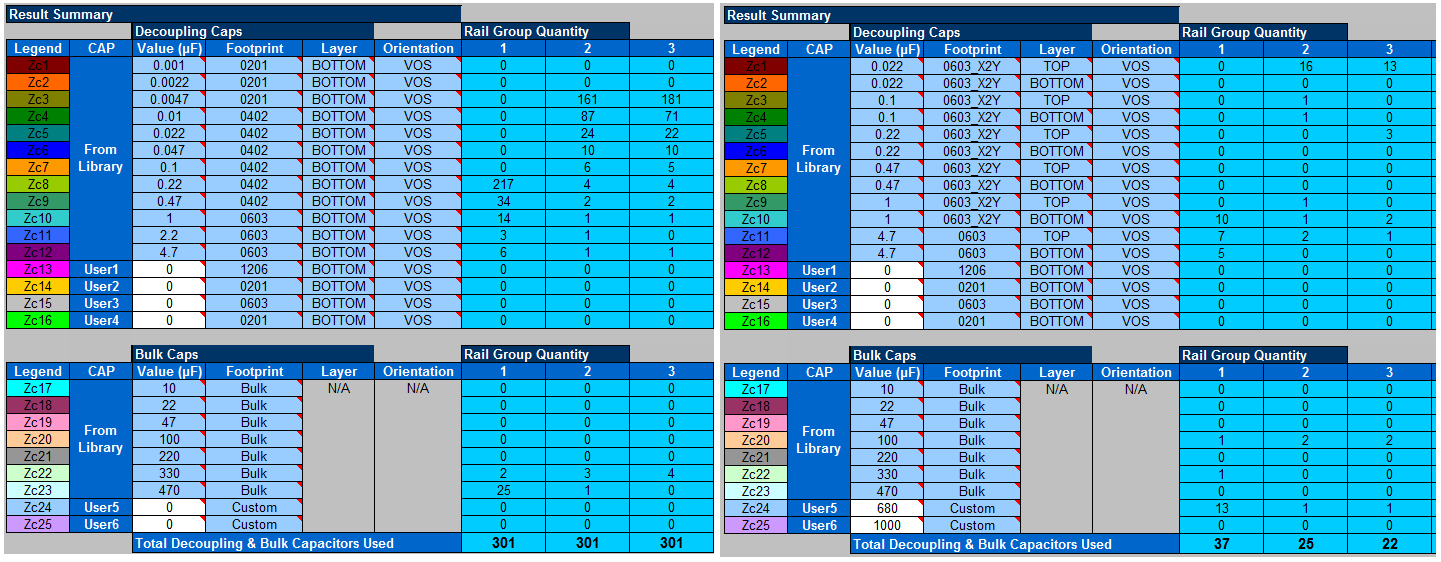

以下图表对比PDN工具原始(左)和最终(右)需要用于VCC,VCCT_GXB,和VCCR_GXB电源的电容器数目。

以下图表对比VCC,VCCT_GXB,和VCCR_GXB电源的原始(顶行)性能与最终(底行)PDN性能。