仅对英特尔可见 — GUID: kux1474989214282

Ixiasoft

产品终止通知

1. Intel® FPGA SDK for OpenCL™ Pro Edition最佳实践指南介绍

2. 查看您Kernel的report.html文件

3. OpenCL内核设计概念

4. OpenCL内核设计最佳实践

5. 分析(Profiling)您的内核来识别性能瓶颈

6. 提高单个Work-Item内核性能的策略

7. 提高NDRange内核数据处理效率的策略

8. 提高存储器访问效率的策略

9. 优化FPGA面积使用的策略

10. 优化英特尔 Stratix 10 OpenCL设计的策略

11. 提高主机应用程序性能的策略

12. Intel® FPGA SDK for OpenCL™ Pro版最佳实践指南存档

A. Intel® FPGA SDK for OpenCL™ Pro版最佳实践指南修订历史

仅对英特尔可见 — GUID: kux1474989214282

Ixiasoft

5.8.5. 无停顿、高占用量百分比和低带宽

内核设计的结构可能会阻止其利用加速器板上提供的所有可用带宽。

切记: 理想的内核流水线条件是停顿百分比为0%,占用量百分比为100%,带宽等于板级可用带宽。

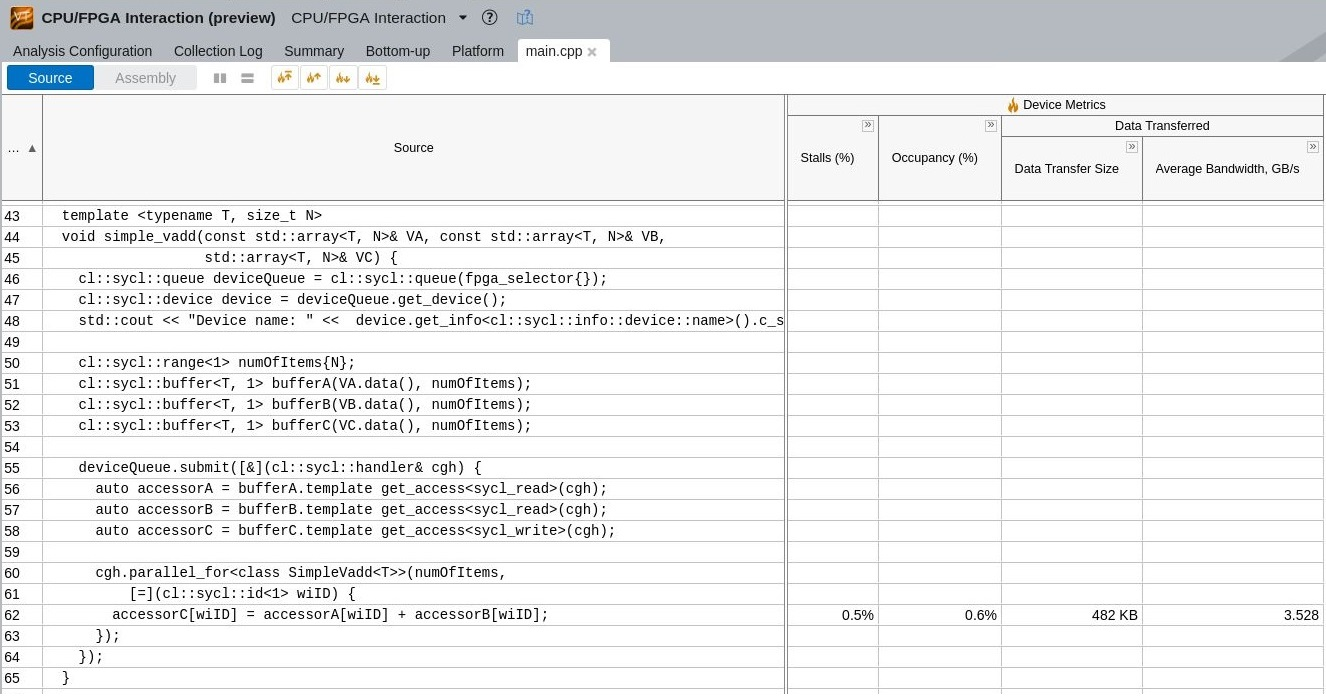

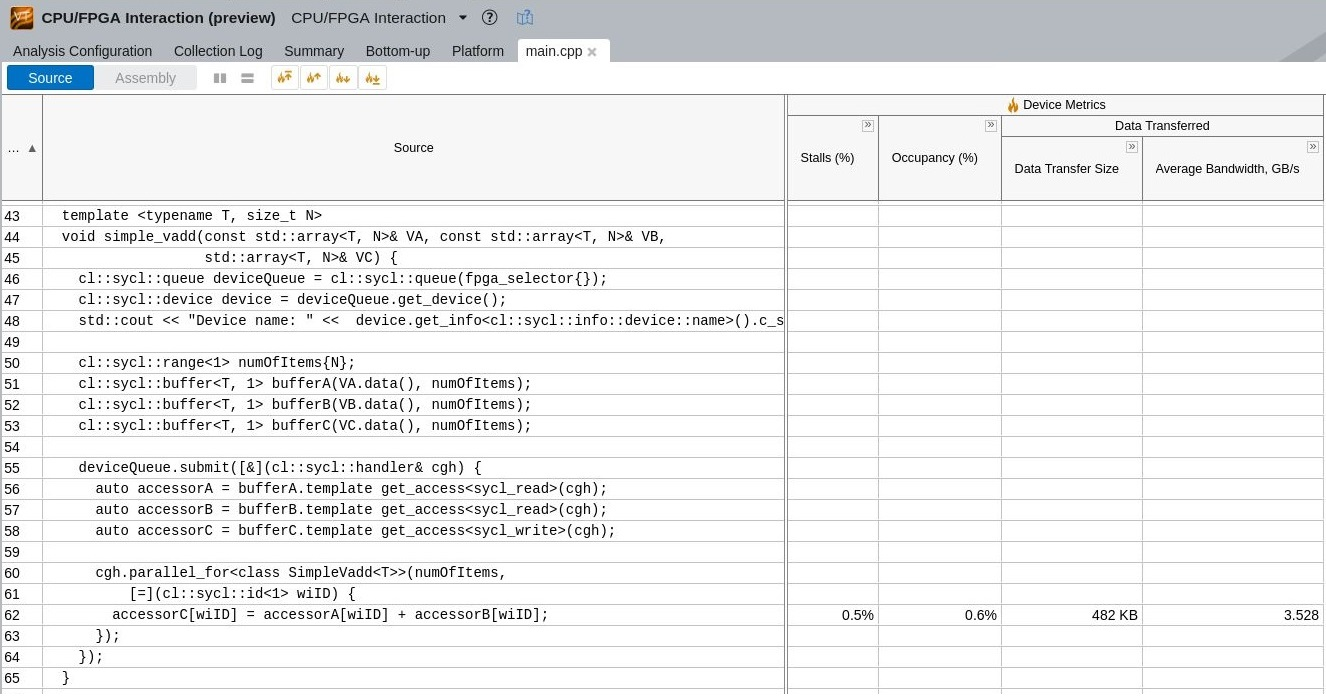

图 74. 示例OpenCL内核和Profiler分析

该示例中,加速器板可以提供25600兆字节/每秒(MB/s)的带宽。但是,vector_add内核正在请求的量是(2次读取+ 1次写入) x 4字节x 294 MHz = 12字节/周期x 294 MHz = 3528 GB/s,这只是可用带宽的14%。要增加带宽,请增加每个时钟周期中执行的任务数。

低带宽的解决方案:

- 自动或手动矢量化内核以wider(加宽)请求

- 展开最内层循环以在每个时钟周期发出更多请求

- 将某些任务授权给另一个内核