仅对英特尔可见 — GUID: cia1637629938085

Ixiasoft

1.4. 性能设计实例的功能描述

性能设计实例旨在展示用于PCI Express Hard IP的P-Tile Avalon-ST的性能。它可以配置为发送存储器只写TLP,存储器只读TLP,或者存储器写入和存储器读取TLP以进行吞吐量测试。吞吐量计数器以FPGA Application逻辑实现,来最大限度地减少软件开销。对于吞吐量测量,在主机侧运行的软件应用程序将发出存储器读TLP并获得从控制寄存器来的吞吐量计数器值,然后在系统终端打印吞吐量数字。需要软件应用程序向控制寄存器发布存储器写,以在测试结束时停止通信量。

性能设计实例自动创建 Intel® Quartus® Prime软件中仿真和编译的必要文件。它支持Gen4 x16,512-bit接口Hard IP模式。对于 Intel® Agilex™ 器件系列,该设计实例支持最高达到500MHz PLD时钟频率。对于 Intel® Stratix® 10 DX器件系列,它支持最高达到400MHz PLD时钟频率。

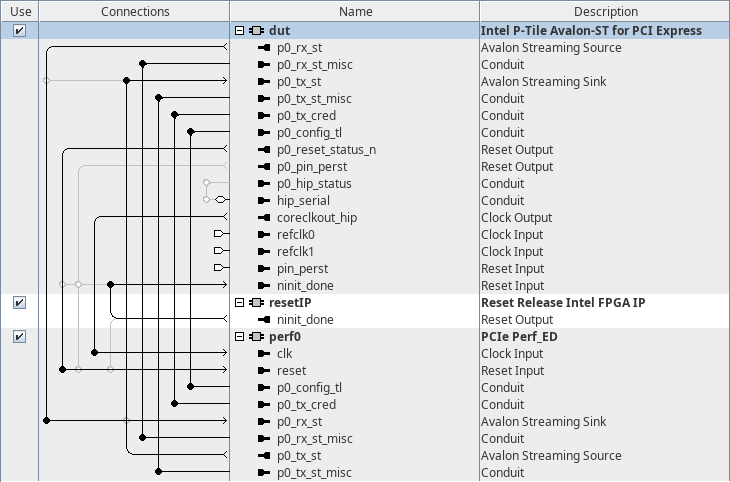

- 按照您指定的参数生成的P-Tile Avalon Streaming Hard IP Endpoint实例(DUT)。该组件与PCIe链路另一端的根复合体\交换机交互,并将从PCIe链路来的数据转换为Avalon-ST数据格式,或反之亦然。

- PCIe Perf_ED (perf0) 组件生成需要的数据通信量以便吞吐量测试。它有以下子模块组成:

-

pioperf_multitlp_adapter (Avalon-ST Interface Adapter)模块将Avalon-ST接口的2段(2-segment )数据转换成Avalon-ST数据的两个单段(single-segment)流。

pioperf_rx_diverter模块将从主机和完成TLP来的存储器写或存储器读TLP分别转向到它们各自目的地以进行进一步处理。

pioperf_rx_intf (RX接口)模块将从pioperf_rx_diverter模块来的TLP头和数据进行解码。它还提取需要的信息来构建完成数据的TLP头,例如请求器ID、标记、属性、tc和字节数,并将它们传递到pioperf_tx_intf以便进一步处理。

pioperf_tx_intf (Tx接口)模块将从pioperf_rx_intf和pioperf_dma_top模块来的请求转换成TLP,并将它们发送到P-Tile Avalon Streaming Hard IP。它以这种简化加权循环方式,通过优先级方案传输TLP:完成TLP > 存储器读TLP > 存储器写TLP。

pioperf_dma_top (DMA_TOP)模块生成存储器写和存储器读请求,并根据控制寄存器中的信息将它们传递给pioperf_tx_intf模块。每个存储器读请求都将被标记为超时之前希望完成的数据,以确保数据完整性。存储器写和存储器读TLP的发布将建立起PCIe链路TX和RX接口处的通信量。其中包含的吞吐量计数器将分析系统中的整体吞吐量。

-

- Reset Release IP:该IP将控之电路保持为复位状态直到器件完全进入用户模式。FPGA置位INIT_DONE输出以指示器件已进入用户模式。Reset Release IP生成逆向的内部INIT_DONE信号以创建您可以用于设计的nINIT_DONE输出。nINIT_DONE信号为高电平直到整个器件进入用户模式。nINIT_DONE置位(低电平)后,所有逻辑处于用户模式并正常运行。您可以按照以下方式之一使用nINIT_DONE信号:

- 门控外部或内部复位。

- 门控到收发器和I/O PLL的复位输入。

- 门控设计块的写使能,例如嵌入式块、状态机和交换寄存器。

- 同步驱动设计中的寄存器复位输入端口。