仅对英特尔可见 — GUID: prr1651627043921

Ixiasoft

2.4.5.1. ebfm_barwr处理过程

2.4.5.2. ebfm_barwr_imm处理过程

2.4.5.3. ebfm_barrd_wait处理过程

2.4.5.4. ebfm_barrd_nowt处理过程

2.4.5.5. ebfm_cfgwr_imm_wait处理过程

2.4.5.6. ebfm_cfgwr_imm_nowt处理过程

2.4.5.7. ebfm_cfgrd_wait处理过程

2.4.5.8. ebfm_cfgrd_nowt处理过程

2.4.5.9. BFM配置处理过程

2.4.5.10. BFM共享存储器访问过程

2.4.5.11. BFM日志和消息过程

2.4.5.12. Verilog HDL格式化函数

仅对英特尔可见 — GUID: prr1651627043921

Ixiasoft

2.3.1.4. Xcelium* 仿真器

注: Xcelium* 仿真器仅适用于具有如下OPN编号的器件:

- AGIx027R29AxxxxR3

- AGIx027R29AxxxxR2

- AGIx023R18AxxxxR0

- AGIx041R29DxxxxR0

- AGIx041R29DxxxxR1

执行以下步骤以通过命令行执行仿真:

- 导出如下环境变量:

- export CADENCE_ENABLE_AVSREQ_6614_PHASE_1=1

- export CADENCE_ENABLE_AVSREQ_12055_PHASE_1=1

- 更换到仿真工作目录:cd <my_design>/pcie_ed_tb/pcie_ed_tb/sim/xcelium

- 执行以下命令:sh xcelium_setup.sh USER_DEFINED_VERILOG_COMPILE_OPTIONS="-sv\ “ USER_DEFINED_ELAB_OPTIONS="-timescale\ 1ns/1ps” USER_DEFINED_SIM_OPTIONS="-input\ @run” TOP_LEVEL_NAME="pcie_ed_tb.pcie_ed_tb" | tee simulation.log

注: 上述命令是单行命令。

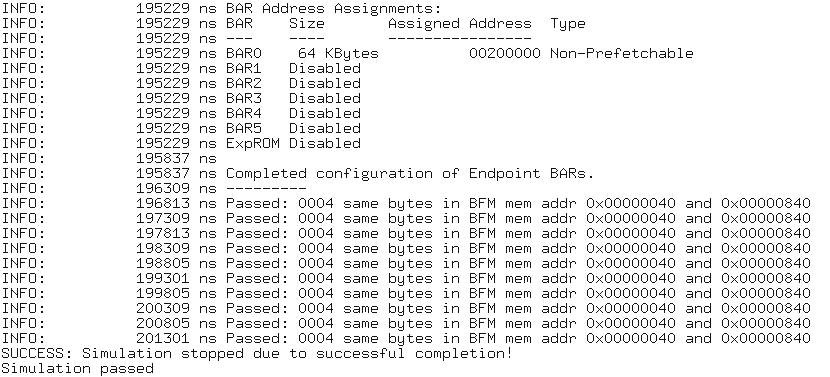

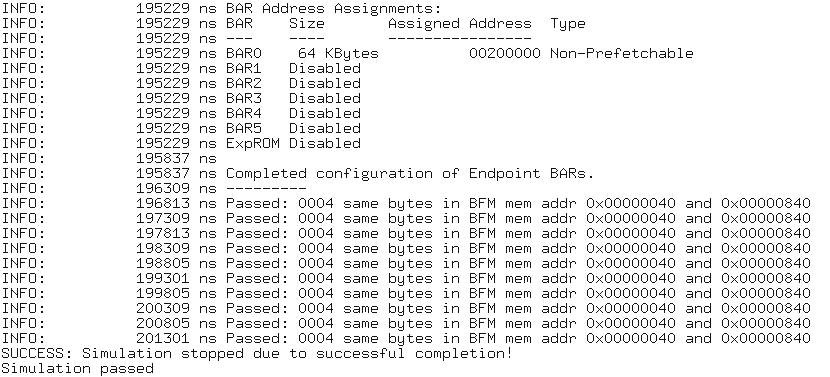

成功的仿真,将包含如下信息:"Simulation stopped due to successful completion!"

图 21. 成功仿真的消息