仅对英特尔可见 — GUID: puc1508901516211

Ixiasoft

4.2.2. Unroll Loop(展开循环)

展开循环后,循环的每个迭代都会在硬件中被复制,并且如果是独立迭代,则将同时执行。展开循环以增加FPGA中的使用面积来减少组件中的延迟。

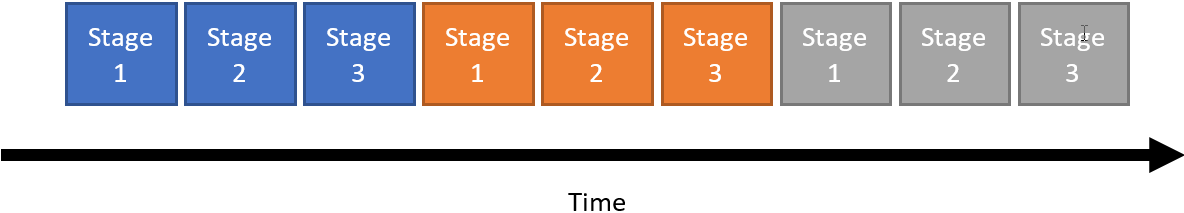

以如下具有3个阶段3次迭代的基础循环为例。每个阶段代表一个时钟周期内循环中发生的操作。

图 8. 具有3个阶段和3次迭代的基础循环

如果该循环的每个阶段需要一个时钟周期来执行,则该循环的延迟为9个周期。

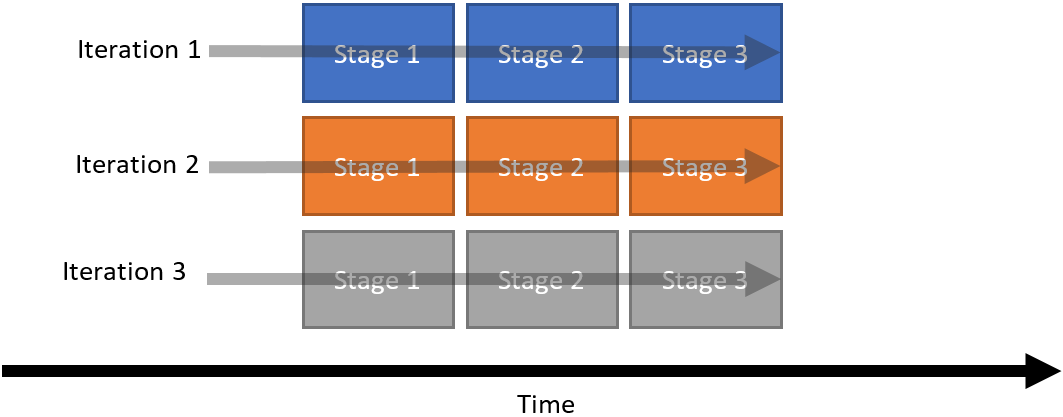

下图显示图 8中展开三次的循环。

图 9. 具有3个阶段和3此迭代的展开循环

现在仅需3个时钟周期即可完成循环的3次迭代,但却需要三倍的硬件资源。

可使用#pragma unroll指令控制编译器如何展开循环,仅当编译器事先知道循环的跳变数或指定了展开因子时,此命令才有效。除了复制硬件之外,编译器还会重新安排电路时间,以使每个操作在准备好输入后立即运行。

有关使用#pragma unroll指令的实例,请参阅 best_practices/resource_sharing_filter教程。