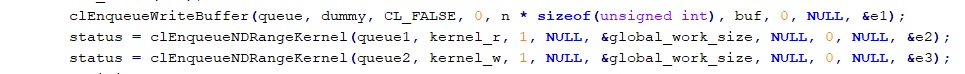

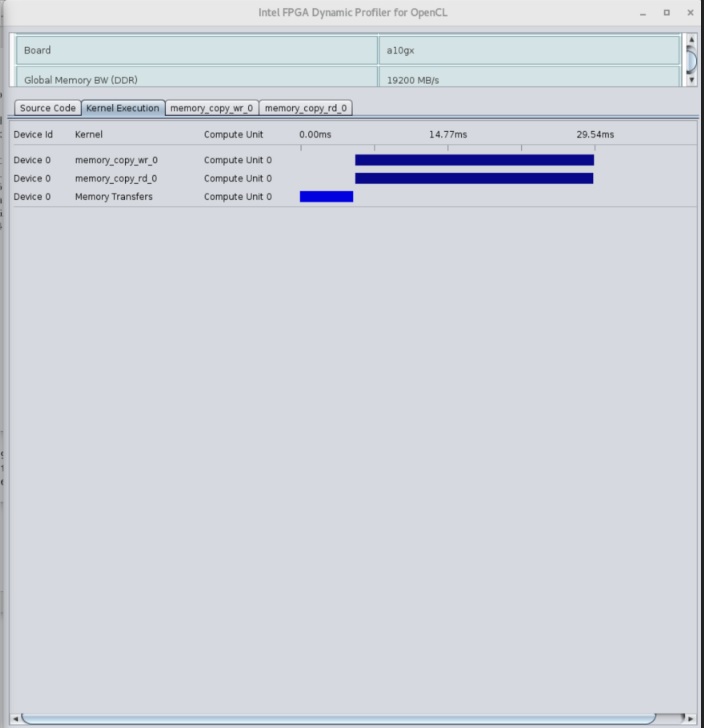

由于面向 OpenCL 的英特尔® FPGA SDK 版本 19.1 和 19.2 出现问题™,在运行 OpenCL™ 设计时,客户可能会发现,即使主机代码之间不存在依赖性,内核执行和内存数据传输也无法同时运行。下面是一个示例,clEnqueueWriteBuffer 和 clEnqueueNDRangeKernel 之间不存在事件依赖性,并且使用不同的命令队列来创新这些命令。但在配置文件报告中,它显示了内核执行和数据传输的运行顺序,而不是并行运行。

这是因为用于 OpenCL 的英特尔® FPGA SDK 19.1 和 19.2 版本的错误™导致内核延迟启动,而此时主机和内核出现了并发 DDR 访问。即使内核和主机访问 DDR 内存的不同部分,内核启动也被延迟。

对内核启动的不正确依赖已在面向 OpenCL 的英特尔® FPGA SDK 的版本 19.3 中修复™。