# 3D LUT Intel® FPGA IP

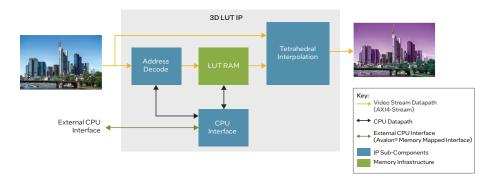

3D look-up tables (LUTs) Intel® FPGA IP provide an efficient solution for video colorspace and dynamic range conversions, chroma-keying, and the creation of artistic effects.

Increased Brightness

Hue Rotation

Hue Rotation

3D LUT Intel FPGA IP provides an efficient solution for video color-space conversions and conversion between nonlinear gamuts. This IP also enables many other artistic and cinematic effects, such as sepia tone, monochrome, color changes, vintage, vivid color, cool/warm film and the ability to create chroma-keys to separate foreground from a colored background. The 3D LUT IP employs Tetrahedral interpolation. The 3D LUT IP uses the most significant bits (MSBs) of the 3-color component inputs to retrieve data values from the contents of the LUT (in FPGA memory), and the least significant bits (LSBs) to interpolate the final output value.

The interpolation processes and memory methods used in Intel's 3D LUT IP use a lower number of gates and memory than competing solutions, enabling practical 3D LUT implementations using an FPGA for a more cost-effective solution. The low resource count and industry standard interfaces such as AXI4-Streaming and AXI4-Lite allow the IP to be easily integrated into your Intel® FPGA design.

## **Applications**

- Color Space Conversions, e.g., HD Rec 709 to UHD Rec 2020

- · Color Correction Film/Video Post Production

- Chroma Keying Virtual Studios, graphics overlays

- Color replacement TV commercials, medical imaging

- Dynamic Range Conversions (SDR-HDR)

- Artistic effects, e.g., sepia tone, monochrome, color-space volume adjustments

## **Key Features**

- Support for 17<sup>3</sup>, 33<sup>3</sup> and 65<sup>3</sup> LUTs

- Support 3 and 4 output channels from the LUT (Alpha / key channel)

- · High quality tetrahedral interpolation

- · Independently set input/output pixel depth

- · Independently set LUT precision

- Dynamic update of table values with optional double buffering to enable clean synchronous switching to a new LUT

- · Includes '.cube' file format conversion utility

- Support for 8, 10, 12 and 16 bit per color component

- Support up to 4 pixels in parallel (PIP) per clock processing

- Low subframe latency (21 clock cycles)

- Support resolutions up to 4K at 60 fps on Intel<sup>®</sup>C10/A10/ S10 FPGAs and up to 8K at 60 fps on Intel Agilex<sup>®</sup> FPGAs

- · Low FPGA resource utilisation

- AXI4-Stream video I/O interface

- AXI4-Stream

⇔ Avalon-Stream Protocol Converters

- Avalon® Memory-Mapped CPU control and memory interfaces

#### **Customer Benefits**

- Low resource yielding lower power 'Edge' implementations

- Free Intel® FPGA IP Evaluation Mode

- Design example available in Intel Resource and Design Center

- Avalon® or AXI interfaces

- · Fully maintained and supported by Intel

#### **Supported Devices**

- Intel® Cyclone® 10 GX FPGAs

- Intel® Arria® 10 FPGAs

- Intel® Stratix® 10 FPGAs

- Intel Agilex® FPGAs

## **Design Your Product Today with Intel FPGAs**

Intel provides a large range of complementary and modular IP cores for video processing and connectivity. These IP cores can be used to create complete solutions for applications in Studio Broadcast, ProAV, Aerospace/Defense, Medical, Consumer, Automotive, Machine vision, and more.

More information is available about Intel video IP at www.intel. com/content/www/us/en/broadcast/products/programmable/overview.html or contact an Intel sales representative.

## **Design Example**

Intel® Arria® 10 GX Development Kit with Bitec HDMI FMC daughter card. Fully compatible with Intel IP cores.

## Typical Resource Usage - Single Buffer

| PIP | Bits per<br>color | LUT Size | ALMs  | M20K | DSPs |

|-----|-------------------|----------|-------|------|------|

| 1   | 8                 | 173      | 810   | 17   | 6    |

| 2   | 10                | 173      | 1,640 | 33   | 12   |

| 2   | 10                | 333      | 1,649 | 120  | 12   |

| 2   | 10                | 653      | 2,575 | 830  | 12   |

Figures for Intel Arria 10 FPGA with video clock FMAX of 300 MHz.

## Typical Resource Usage – Double Buffer

| PIP | Bits per<br>color | LUT Size | ALMs  | M20K  | DSPs |

|-----|-------------------|----------|-------|-------|------|

| 1   | 8                 | 173      | 937   | 25    | 6    |

| 2   | 10                | 173      | 1,681 | 49    | 12   |

| 2   | 10                | 333      | 1,685 | 224   | 12   |

| 2   | 10                | 653      | 4,035 | 1,622 | 12   |

#### **Useful Links**

- Intel FPGA 3D LUT Design Example Requires Intel Resource & Design Center access

- Intel® Arria® 10 GX FPGA Development Kit

- Intel Agilex® 7 FPGA Development Kit

- · Bitec HDMI FMC daughter card

Intel technologies may require enabled hardware, software or service activation. No product or component can be absolutely secure.

Your costs and results may vary.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

SS-1138-1.2

2

Intel Confidential